Introduction

Printed circuit boards (PCBs) are essential components in electronic devices and equipment. They provide the mechanical support and electrical connections between the various components that make up an electronic circuit. A key aspect of PCB design is routing – determining the paths and channels through which signals travel from one component to another on the board. Proper routing is critical for the reliable functioning of a circuit. This article will provide a comprehensive overview of the key routing rules and best practices that PCB designers need to follow to create functional and optimal board layouts.

Basic Routing Principles

Routing on a PCB involves tracing out conductive pathways, referred to as traces, that connect different components and devices together. Some fundamental guidelines underpin all routing activity:

Minimize trace length

Shorter trace lengths are preferable as they reduce resistance and chances of noise pickup and interference. Lengthy traces can cause signal degradation unless width is increased to compensate.

Avoid acute angles

Traces should follow paths with gentle bends and curves instead of sharp, right-angled turns. Sharp corners cause impedance mismatch and signal reflections.

Use 45/90 degree angles

When inevitable, right angle turns should be precisely 45 or 90 degrees to minimize impedance discontinuity.

Equal trace lengths

Lengths should be matched when routing signals in parallel between components to prevent skew.

Minimize vias

Vias are conductive holes connecting traces between layers. Excessive vias introduce impedance disruptions. Use just enough vias to route efficiently.

No acid traps

Avoid creating small gaps or holes surrounded by copper that can trap acid during manufacturing.

Symmetric layout

Maintain symmetry and balance when routing around components. This improves layout aesthetics.

Trace Width Rules

Trace width is a critical routing parameter impacting current capacity, impedance control and manufacturability. Some key rules guide trace width selection:

Match impedance

Choose width to match the characteristic impedance of the route for efficient signal transfer.

Limit temperature rise

Wider traces handle more current without excessive heating. Narrower traces may overheat at high currents.

Accommodate manufacturing

Trace width must allow for tolerances of board fabrication process. Too thin or too thick traces will be difficult to produce reliably.

Meet safety directives

Certain applications like medical and automotive products require minimum trace widths by regulation.

High-speed design rules

Widths may need adjustment to control impedance for high-frequency signals.

Balance current

When signals share a common return path, size widths identically for optimal current sharing.

High voltage tracing

Use exceptionally wide traces or parallel traces when routing high voltage lines to safely handle large currents.

Component spacing

Leave adequate clearance between traces for spacing between lead pads or pins.

Antenna effect reduction

Increase widths of traces attached to high impedance inputs/outputs to dampen antenna effects.

Trace Routing Styles

There are three predominant routing styles used by PCB designers:

Point-to-point routing

Each connection is routed individually in the most direct path possible between endpoints. This allows full control over routing but is time consuming for complex multi-signal layouts.

Rectilinear routing

Traces only run parallel or perpendicular to the edges of the board. This pattern-based approach makes layout fast and orderly but can result in sub-optimal trace lengths.

Autorouting

Software automatically handles all trace routing based on supplied rules and parameters. This is very fast but the software cannot optimize trace paths like a skilled designer. Autorouting still requires manual review and tweak of the generated traces.

Here is a comparison of the different trace routing styles:

| Routing Style | Speed | Control | Optimization |

|---|---|---|---|

| Point-to-point | Slow | Full | Maximum |

| Rectilinear | Fast | Minimal | Low |

| Autorouting | Very Fast | Configurable | Moderate |

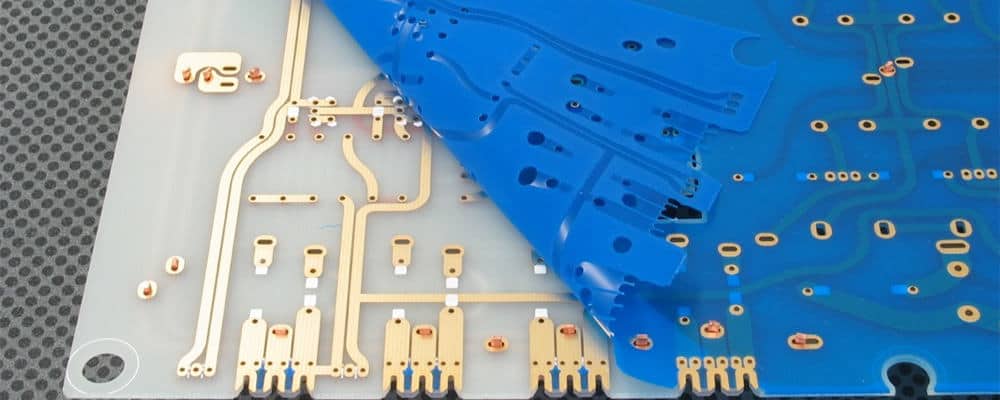

Trace Routing Layers

Most PCBs use multiple copper layers separated by insulating dielectric material. Routing is distributed between layers, following these guidelines:

- Use outer layers for high-speed signals requiring controlled impedance. The continuous reference planes provide consistent impedance.

- Route critical traces on inner layers for shielding when the boardstack allows it.

- Distribute ground fills evenly on multiple layers. This lowers ground noise by reducing common impedance.

- Route layers in one direction only (horizontal or vertical) when possible, for orderly trace layout.

- Avoid routing multiple signals in parallel between layers. This can cause crosstalk coupling. Route orthogonally instead with vias.

- Assign power and ground traces to their own inner layers when designing high layer-count boards to simplify layout.

Here is a typical 4-layer board stackup showing trace routing allocation:

| Layer | Purpose |

|---|---|

| Top | High-speed signals |

| Layer 2 | Ground plane |

| Layer 3 | Power plane |

| Bottom | Mixed signals |

Trace Routing Sequence

Follow a logical sequence when routing traces on a board:

- Route critical high-speed or high-current traces first. These require special attention to width, spacing and impedance control.

- Route traces from drivers to immediate loads before fanning out to other loads. This clusters associated traces together neatly.

- Route traces on inner layers before outer layers. Inner traces often connect between outer layer paths.

- Route ground and power traces next to provide returns paths for signals.

- Complete any auto-routed traces manually for impedance or length tuning.

- Route remaining low-speed traces using clean point-to-point connections.

- Optimize routings with post-layout tweaks to length matching, crosstalk minimization and noise reduction.

Trace Spacing Rules

Adequate spacing between traces, planes and pads ensures both design reliability and manufacturability. Key spacing guidelines include:

- Maintain 2-3x dielectric thickness spacing between traces for impedance control and crosstalk prevention.

- Use wider spacing between traces when dielectric thickness or variance is high.

- Space traces from board edges by at least the width of the trace.

- Provide larger spacing near connectors for cabling considerations.

- Allow 1.5x larger than usual spacing for hand soldering.

- Follow manufacturer’s clearance rules between copper and board edges or cutouts.

- High voltage traces require very large spacing for creepage clearance.

- Prevent traces from overlapping split power or ground planes.

- Watch for acid traps created by insufficient spacing around traces.

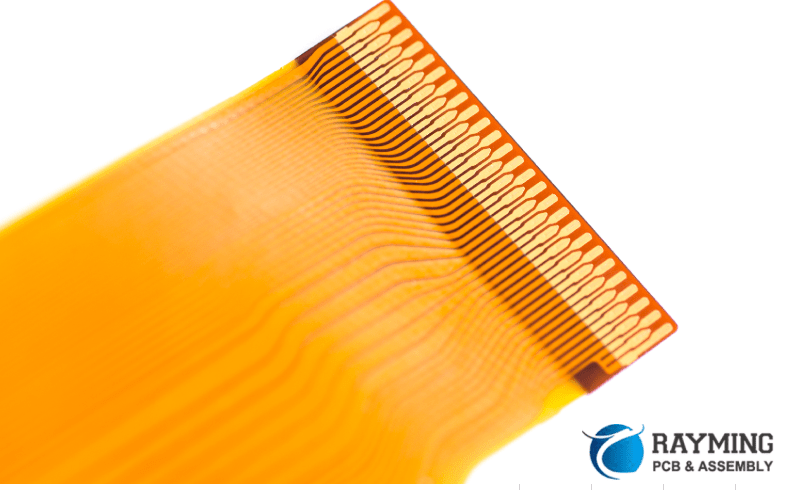

Length Matching Techniques

Matching the lengths of traces in a parallel bus ensures simultaneous signal arrival, preventing data skew. Common length matching approaches are:

- Routing traces in a sawtooth pattern so cumulative lengths are identical.

- Adding small meanders or loops at the end of shorter traces.

- Using clockwise and counter-clockwise turning serpentine patterns.

- Adding empty pads as capacitive loads along shorter traces to delay signals.

- Utilizing vias or detours to zigzag longer paths into matching shorter ones.

- Intentionally necking down trace widths can slow signals as an alternative to physical length changes.

Crosstalk Prevention Techniques

Electromagnetic coupling between adjacent traces causes crosstalk distortion. Use these strategies to minimize crosstalk:

- Increase spacing between traces, or use ground fills to isolate traces.

- Route victim and aggressor signals on different layers orthogonally.

- Avoid routing buses with fast switching signals in parallel over long distances.

- Make adjacent traces perpendicular instead of parallel to reduce coupling.

- Use wider spaces between parallel signal layers or ground fills to shield traces.

- Minimize common impedance paths shared by multiple signals.

- Limit parallel runs to under 0.5″, keeping overall parallel length low.

- Tune trace widths, spacing and impedances to reduce coupling.

- Add ground vias along parallel traces to isolate them using continuous guards.

Power Delivery Network Routing

The power distribution traces must properly conduct current across the PCB. Follow these guidelines:

- Use as large a trace width as space allows for power traces, for reduced resistance.

- Provide multiple vias when crossing power traces between layers to reduce via resistance and inductance.

- Split power nodes into area fills on multiple layers to share high return currents.

- Connect decoupling capacitors directly between IC power/ground pins and supply rails to absorb noise.

- Ensure uniform power trace widths and symmetric splitting for even voltage distribution.

- Isolate sensitive analog and digital sections into separate power islands to prevent noise coupling.

Mixed Signal Routing Guidelines

Boards with both analog and digital signals require special care to prevent interference:

- Route analog and digital signals on separate board sections or layers. Insert ground fills between them.

- Shield clock lines, high-speed digital traces, or other noisy signals to contain EMI.

- Use star distribution topology to route clock signals radially instead of as buses.

- Avoid gaps in ground layers under mixed signal areas. Use stitching vias to connect ground fills between layers.

- Increase isolation between traces with more spacing or guard traces according to frequency.

- Provide separate ground returns for sensitive analog signals to keep paths isolated.

High-Speed Design Techniques

High-frequency signals demand careful routing to prevent signal degradation:

- Match trace impedances and minimize discontinuities. Use very wide traces if necessary.

- Limit stubs, vias or branches along transmission line routes. These cause reflections.

- Provide uninterrupted ground planes adjacent to transmission lines for controlled impedance.

- Use differential trace routing with tight coupling and precise length matching between lines.

- Add termination resistors at route ends to absorb signals and prevent reflections.

- Reduce parallel trace coupling with shielding ground planes above and below traces.

- Utilize QFN packages with exposed thermal pads for low inductance chip-board interconnect.

Final Design Rule Checks

Before design signoff, audit the PCB layout against the checklist below:

- Verify all traces are routed completely from pad to pad with no opens or unfinished connections.

- Check trace widths and clearances conform to specifications set out in design rules.

- Confirm length matching, crosstalk, and EMI control measures are applied appropriately.

- No acid traps exist that can jeopardize manufacturing.

- Components are placed for optimal routing, not creating unnecessary detours.

- Impedance requirements are satisfied through trace geometries.

- Traces carrying high current have adequately low resistance.

- Maximum current density levels for traces are not exceeded for tolerable heating.

- All design for manufacturing (DFM) guidelines provided by the board fab are satisfied.

- There are no unrouted nets or signals left requiring connections.

Conclusion

Skillful routing creates a PCB layout that is high-performing as well as manufacturable. Following standard routing practices and design rules helps achieve a functionally optimal, quality PCB design. Usage of appropriate trace widths, spacing, matching, layering, isolation and impedance control techniques combined with careful validation ensures that the routed board performs reliability under all operating conditions. Adhering to the key guidelines outlined here will enable PCB designers to produce robust, error-free routing of traces.

Frequently Asked Questions

What are the most important routing considerations for a reliable PCB?

The most crucial routing practices for reliability are impedance matching through trace geometries, minimizing trace lengths, preventing crosstalk and EMI through proper isolation and grounding, length matching parallel traces, allowing adequate trace spacing and widths, and symmetry in power delivery traces.

How can I tell if my PCB routing needs improvement?

Signs of poor routing include acid traps, incomplete connections, excessive vias, impedance mismatches, right-angled traces, unshielded parallel traces, overloaded power traces, and deviation from ground plane clearances or manufacturer DFM rules. These issues should be addressed through rerouting.

What are some common routing mistakes to avoid?

Frequent mistakes are not matching net trace lengths, inadequate trace spacing leading to shorts, routing too close to edges without clearance, sharp trace corners, routing multiple signals in parallel on adjacent layers, not shielding or isolating high-speed traces, and asymmetric power distribution networks.

Should I use autorouters or route the PCB manually?

Autorouters can quickly generate complex routing but usually require extensive manual checking and rework to optimize trace lengths, spacing, impedance and manufacturability. Manual routing takes more time but allows full control over the quality of the routing. A combination approach is most efficient.

How can I reduce crosstalk between parallel PCB traces?

Use wider trace spacing, route on different layers, interleave grounds between traces, limit parallel run lengths, make traces perpendicular instead of parallel where possible, adjust trace widths or spacing, add ground guard traces, utilize shielding ground planes, and minimize common return current paths.

Leave a Reply