Noise Figure and Sensitivity

The primary purpose of an LNA is to amplify weak signals with minimal added noise. Therefore, achieving a low noise figure (NF) is a top priority in LNA Design. The noise figure quantifies how much the signal-to-noise ratio (SNR) degrades as the signal passes through the LNA. A lower NF means the LNA introduces less noise and better preserves the signal integrity.

NF is related to sensitivity, which is the minimum signal level the receiver can reliably detect. Sensitivity is a key metric in wireless systems like cellular base stations, GPS receivers, and IoT devices. To maximize sensitivity, the LNA should have the lowest possible NF.

Some practical tips for minimizing NF in LNA design:

- Choose a low-noise transistor (e.g. GaAs pHEMT, SiGe HBT) with minimal parasitics

- Optimize source impedance matching for minimum noise

- Minimize losses in input matching network

- Avoid resistive feedback and emitter degeneration

- Use noise matching techniques like inductive source degeneration

- Minimize DC power consumption while maintaining gain

Gain and Linearity Trade-offs

While a high gain is desirable to amplify weak signals, too much gain can degrade linearity. Non-linearity creates distortion in the form of harmonics and intermodulation products.

In LNA design, there is often a trade-off between noise figure, gain, and linearity. Increasing the bias current improves linearity but also increases power consumption and potentially degrades noise figure. The converse is also true – decreasing bias current improves noise figure and reduces power but degrades linearity.

The LNA designer must balance these competing factors based on the specific requirements. If linearity is a top priority, active bias control and linearization techniques can be used. If power consumption is critical, lower supply voltages and bias currents are necessary.

Some other tips for managing gain and linearity:

- Perform load-pull analysis to find optimal load impedance for gain and linearity

- Use Volterra series analysis to predict and optimize linearity

- Apply derivative superposition method to improve linearity

- Implement an automatic gain control (AGC) loop for constant output power

- Use cascaded stages with inter-stage matching for higher gain

Input and Output Matching

Impedance matching is critical in LNA design for maximum power transfer and minimal reflections. The input of the LNA should be matched to the source (often 50Ω) for minimum noise, while the output is usually matched for maximum gain.

Matching network design requires careful selection of component values (inductors, capacitors) to achieve the desired impedance transformation over the frequency band of interest. The quality factor (Q) of the matching components impacts the bandwidth and insertion loss.

Some practical considerations for LNA input and output matching:

- Use Smith Chart and S-parameters to visualize and optimize impedance matching

- Design matching networks with sufficient bandwidth to cover desired frequency range

- Realize matching networks with high-Q components to minimize losses

- Consider PCB layout parasitics when designing and optimizing matching networks

- Perform EM simulations to model actual component behavior at high frequencies

- Use on-chip matching if possible to minimize PCB losses and variations

Stability Analysis

Stability is a critical consideration in LNA design. Unstable amplifiers can oscillate, causing system failure and even damage. LNAs can be prone to instability due to high gain and potential feedback paths created by parasitics.

Stability analysis involves checking the LNA at all frequencies to ensure it will not oscillate under any load conditions. The two main stability metrics are the Rollett stability factor (K) and the stability measure (B1). For unconditional stability, K > 1 and B1 > 0 at all frequencies.

Some tips for ensuring LNA stability:

- Check stability at all frequencies, not just the operating band

- Add a shunt resistor to the output to improve stability at the expense of gain

- Use neutralization capacitor to cancel feedback and improve stability

- Perform Monte Carlo simulations to check stability under component variations

- Do stability analysis under mismatch conditions (VSWR)

- Consider stability versus temperature if needed for the application

Biasing and Power Consumption

LNA biasing involves setting the DC operating point of the transistor for the desired performance. Typically this means selecting the supply voltage and bias current.

The bias point affects key parameters like gain, noise figure, linearity, and power consumption. In general, higher bias currents improve gain and linearity but degrade noise figure and increase power dissipation. The converse is true for lower bias currents.

Power consumption is an important metric in battery-powered wireless devices. LNAs often run continuously so their power adds up. Minimizing LNA power while meeting other specs is a key design challenge.

Some practical LNA biasing tips:

- Use active bias circuits for precise and stable biasing over temperature

- Consider a dual-bias topology for low noise and high linearity modes

- Simulate to find optimal bias point for noise and gain

- Use current mirrors and current steering to improve bias network PSRR

- Monitor supply current as a diagnostic for detecting output shorts and overloads

Layout and Grounding

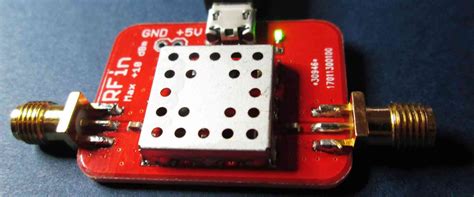

Careful PCB layout and proper grounding techniques are essential for optimal LNA performance. At GHz frequencies, PCB traces behave like transmission lines with associated parasitics and losses that can degrade gain and noise figure if not accounted for.

LNA layout should be compact to minimize parasitics but not so dense as to cause unwanted coupling. Distribute power rails to provide low-impedance paths and avoid feedback. Use microstrip or stripline transmission lines for controlled impedance.

Proper grounding is critical to minimizing ground loops, supply noise coupling, and other unwanted effects. Use a solid ground plane and multiple vias to reduce ground impedance. Separate analog and digital grounds to prevent noisy digital circuitry from coupling into sensitive LNA inputs.

Some PCB layout best practices for LNAs:

- Simulate PCB traces as transmission lines and optimize geometry

- Keep noise-sensitive nodes (e.g. LNA input) away from noisy circuits

- Route power and ground as wide, low-impedance traces

- Avoid routing signals over split ground planes

- Isolate LNA input and output with separate power/ground pins

- Use EM-simulated models for critical components (e.g. inductors, RF transistors)

ESD Protection

LNA inputs connected to external antennas or cables can be exposed to electrostatic discharge (ESD) events that can damage or destroy the sensitive transistors. Implementing adequate ESD protection on LNA inputs is crucial for robustness.

ESD protection devices clamp the input voltage to a safe level when an ESD strike occurs. Discrete ESD diodes or integrated ESD structures can be used. The key is selecting protection devices that can handle the expected ESD levels while minimizing added capacitance that degrades noise and high-frequency performance.

Some ESD protection design tips:

- Use low-capacitance ESD diodes and place them close to LNA input

- Ensure ESD devices turn on fast enough to clamp the input voltage spike

- Perform ESD testing per IEC and JEDEC standards

- Consider LNA performance degradation due to ESD device parasitics

- Protect all pins including RF, DC, and control lines

- Simulate ESD clamps to verify protection and signal integrity

Packaging and Interface

The LNA package and interface can significantly impact high-frequency performance. Bond wires, leads, and pins all introduce parasitic inductance and capacitance that can degrade gain and cause instability if not properly modeled and compensated for.

Surface mount packages like QFN and BGA are preferred for LNAs due to their low parasitics and good thermal dissipation. Flip-chip packaging eliminates bond wires for even better performance. At mm-wave frequencies, specialized packages like wafer-level chip-scale packaging (WLCSP) are used.

The RF input and output should have controlled-impedance (typically 50Ω) connections to the PCB. DC supply and control pins should be decoupled with local bypass capacitors. A ground paddle tied to PCB ground with multiple vias reduces ground bounce.

Some packaging considerations for LNAs:

- Select a package with minimal parasitics and good thermal performance

- Use EM simulations to model package behavior at frequency

- Design input and output for 50Ω and ensure good PCB launches

- Provide separate power and ground pins for RF and DC

- Use multiple ground vias to minimize inductance

- Consider signal coupling between adjacent pins

Integration and Multi-chip Modules

Highly integrated receivers often incorporate the LNA on-chip with the mixer, PLL, and baseband circuitry. This system-on-chip (SoC) approach reduces size and cost but can degrade LNA performance due to substrate noise coupling and limited-Q passives.

Stand-alone LNA chips are still used for the highest performance. GaAs and GaN processes offer superior noise and linearity compared to silicon-based SoCs. Multi-chip modules (MCMs) integrate a discrete LNA with filters, switches, and other front-end components for a compact solution.

At mm-wave frequencies, antenna-in-package designs are popular. These integrate the antenna with the LNA and other chips within a low-loss package. This eliminates PCB losses and allows very wide-band low-noise operation.

Some LNA integration tips:

- Carefully model substrate coupling and layout interactions in SoCs

- Consider a stand-alone LNA for best noise and linearity

- Explore MCM options to minimize board losses and parasitics

- Integrate antenna with LNA at mm-wave for optimal partitioning

- Evaluate different semiconductor processes for performance targets

Measurement and Characterization

Accurate measurement and characterization of LNA performance are essential for verifying the design meets specifications. Key parameters to measure include gain (S21), noise figure (NF), input and output return loss (S11, S22), reverse isolation (S12), P1dB, IP3, and stability (K).

A vector network analyzer (VNA) is used to measure S-parameters and stability. A noise figure analyzer or spectrum analyzer with noise source is used for NF measurements. A power meter or spectrum analyzer measures 1dB compression and IP3.

Proper calibration and de-embedding are critical for accurate measurements. Off-chip parasitics and fixture losses must be removed to get the true LNA performance. Time-domain reflectometry (TDR) is useful for characterizing impedance discontinuities.

Some practical tips for LNA measurements:

- Perform short-open-load-through (SOLT) calibration of VNA at reference planes

- Use on-wafer probing for bare die measurements to minimize parasitics

- De-embed fixture and interconnect losses for packaged parts

- Take multiple averages and use smoothing for NF measurements

- Characterize LNA across frequency, temperature, supply voltage

- Verify nonlinear metrics like P1dB and TOI over input power range

Frequently Asked Questions

-

What is the typical noise figure of an LNA?

A: The typical noise figure of an LNA depends on the frequency, bandwidth, and semiconductor process. For sub-6 GHz applications, LNAs can achieve noise figures of 0.5-2 dB. At mm-wave frequencies, noise figures of 2-5 dB are typical. Highly optimized LNAs can achieve sub-1dB noise figure. -

How much gain should an LNA have?

A: The optimal LNA gain depends on the system requirements and cascade analysis. Generally, 15-25 dB of gain is sufficient to minimize the noise contribution of subsequent stages like the mixer. Too much gain can degrade linearity and cause instability. -

What are the key differences between an LNA and a power amplifier (PA)?

A: An LNA is optimized for low noise figure and moderate gain, while a PA is optimized for high output power and efficiency. LNAs typically have higher linearity than PAs. LNAs are used at the receiver front-end while PAs are used at the transmitter output. -

Can I use an LNA for transmit applications?

A: In general, no. LNAs are designed for receive applications where low noise and moderate linearity are key. For transmit, a power amplifier (PA) is the appropriate choice, as it can deliver the required output power with high efficiency. -

What are some common applications for LNAs?

A: LNAs are used in a wide range of wireless applications including cellular base stations, handsets, GPS receivers, satellite communications, radar, WiFi, Bluetooth, and IoT devices. Any application that requires amplifying very weak RF signals with minimal added noise can benefit from an LNA.

In summary, designing a high-performance LNA requires careful consideration of multiple factors including noise figure, gain, linearity, impedance matching, stability, power consumption, layout, packaging, and characterization. By following the practical design tips outlined in this article, engineers can develop LNAs optimized for their specific application requirements. While there are inherent trade-offs between metrics like noise, gain, and power, a skilled designer can find the right balance to meet system needs.

Leave a Reply